최근 글을 아무것도 안올리고 있었는데,

수학 공부부터 해야할까, 알고리즘-자료구조를 해야할까, 파이썬 프로그래밍 하면서 경험을 쌓을까 등등..

뭘할지를 고민하다가 지금 하고 있는 것들이 조금씩 질리기 시작했고

(하나만 하면 질리니까 여러개를 느리지만 돌아가면서 하곤 있긴했다.)

결국에는 뭐든 만들기 위해서 컴퓨터 구조부터 다시 해보는게 필요하다고 생각이 들었다.

마침 생각난게 전에 하다가 만 nand2tetris

우리나라에서는 아두이노나 라즈베리파이에 비하면 유명하지는 않다.

그렇지만 이 nand2tetris의 가장 큰 매력은 이름 그대로 nand 게이트를 이용해서 hack이라고

비교적 간단한? 구조의 컴퓨터(cpu, memory, registor 등을 하드웨어 시뮬레이션으로 직접 구현한다!)를 만들고

jack이라고 하는 자바 비스무리한 객체지향 언어를 통해 테트리스를 구현하는 내용을 다루고 있다.

나는 일반적인 대학교 컴공과를 나오지는 않고 얼핏얼핏 디지털 논리회로 수업을 듣긴했었는데

처음 디지털 논리회로에 대해서 배울때는 카르노맵까지만 공부했었고, 정보처리기사 자격증 딸때도

이 논리회로가 뭐하는건지 몰랐다! 그냥 게이트에 입력이 어떻게 들어가면 어떻게 나오구나를 진리표대로외우기만 했다.

이 프로젝트에 대해서는 전에 밑바닥부터 시작하는 딥러닝 책에서 보고 알게되면서

우리가 알던 컴퓨터가 논리 게이트로 만들고, 난드게이트만가지고도 컴퓨터를 만들수 있다는것에 놀랐다.

처음 이걸 알았을 당시(4~5년 전쯤)에는 원서를 직접 구입해서 따라가려고는 했었지만

우리나라에는 한글 자료도 없었고, 영어 원서 자료 뿐이다보니 책 한페이지 한페이지를 번역해가면서 보는데

처음에는 1페이지에 3~40분 걸릴만큼 오래걸렸고 힘들어서 포기 하고 말았다.

(2년 전쯤에 이전에 쓰던 블로그를 시작하면서 컴퓨터아나토미 책을 보고 다시 했었던것 같았는데 그때도 가산기인가? 거기까지밖에 가지 못했었다.)

지금이야 남인천 폴리텍 다니면서 그 동안 삽질하면서 영어 실력도 늘고,

전기전자에 대해서 공부하고나서 다시 디지털 논리회로를 보니 보는 눈이 달라지게 되었다.

and니 or 게이트란게 있는데 이전에는 진리표만 알고 있었다면,

지금은 다이오드나 트랜지스터에 대해서 조금이라도 알고나서 이러한 게이트를 어떻게 만드는지를 보니까

그동안 그놈의 게이트 게이트라는게 뭐하는 놈인지 덜 막연해지고 조금은 이해된다고 해야될까.

아무튼 블로그에 올려야지 생각만 하고 귀찬아서 안올렸지만 프로테우스라고 하는 전자 시뮬레이터를 이용해서

jk 플립플롭 가지고 (책을 참고했지만) 동기 카운터도 만들었고 영어 실력도 전보다는 늘었으니까

지금이라면 이 책을 할수 있겠다는 생각이 들었다.

그래서 한동안 이책을 보느라 블로그에 아무것도 올리지도 못하고 있었다.

전보다 영어 실력이 늘었다 해도 원서 보는건 힘들고 오래걸렸다.

기회가 되면 이 프로젝트가 코세라 강의에도 있고 책의 절반 정도(하드웨어 구현)까지는 공개되어있으니까

번역이라도 해볼까 싶다.

코딩 교육한답시고, 아두이노나 라즈베리파이 같은걸로 깔짝깔짝대는것 보다는 유익하다 생각하는데

생각해보니까 처음 코딩 공부할때 해보는게 괜찬은거같네

프로그래밍은 어느정도 땟는데 컴퓨터 구조를 제대로 느껴보고 싶은 사람에게 딱 맞다.

기본 게이트에서 테트리스 게임 만드는 것까지 목표로 하다보니,

한 개념이 나오면 구현에 필요한 정도로만 짧고 쉽게 이야기하고 넘어가는데

어떤 용어가 나오면 그걸 또 어렵게 설명하거나 번역을 엉망으로 해서 이해하기 힘든 책도 많은만큼

정말 영어 원서지만 엉터리 번역서보다 이해하기 훨씬 쉬웠다.

....

글을 적다가 알았는데 번역서가 나왔었네?

책 이름은 밑바닥부터 만드는 컴퓨팅 시스템이다.

아무튼 그건 그렇고 1/3 정도는 이미 그냥 읽었고 영어 공부한다 생각하고 계속 봐야겠다.

책 저자분이 만드신 홈페이지에 가면 이 HACK 컴퓨터를 FPGA로 실제로 구현했다던가

재밌어보이는 프로젝트가 꽤 존재한다.

아무튼 이 책은 두 파트로 나눠져있다.

1. 하드웨어

2. 소프트웨어

여기서 설명하기를 하드웨어 기본 소자인 게이트에서 부터 바닥에서 위로 바텀업식으로 진행하는데

1장에서 게이트

2장에서 조합 논리 회로(가산기, ALU)

3장에서 순차 논리 회로(플립플롭->레지스터->메모리)

4장에서는 기계어와 어셈블리어

5장에서는 CPU, IO장치

까지가 하드웨어 구현에 관한 내용이 되겠다.

이 이후로는 어셈블리어, 가상머신, 운영체제, 객체지향언어 등에 관한 내용이 있는데

아직은 6장 어셈블리어 조금까지만 봤지 뒷 내용은 보지않아서 잘 모른다.

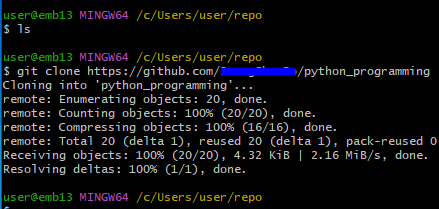

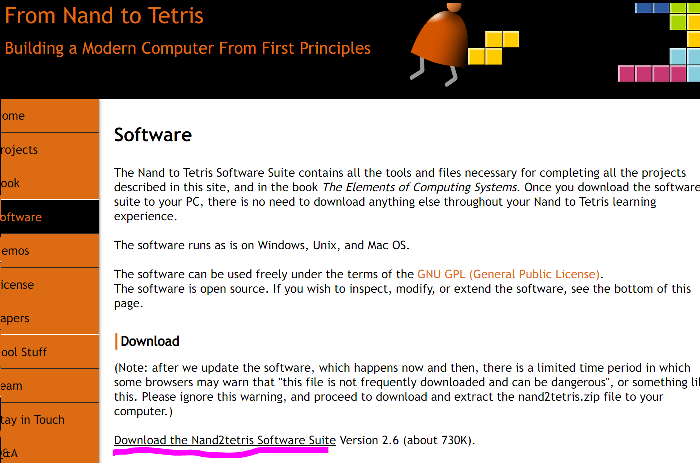

자 그럼 이 프로젝트를 시작하기 위해서 필요한 툴 부터 다운로드 하자

아래의 링크에 들어가면 바로 보인다.

옆에 보면 papers나 demos에서 책/ppt 내용, 그리고 실제로 구현한 내용들을 확인할수 있다.

https://www.nand2tetris.org/software

굳이 여기서는 게이트가 뭔지 설명 하지도 않고, 설명 잘하는 분들도 많은데

진행할수 있는데까지는 대충 진행하는거 올리려고한다.

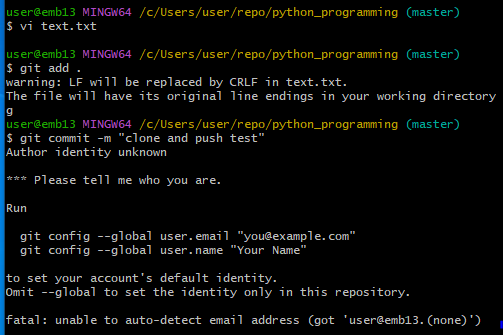

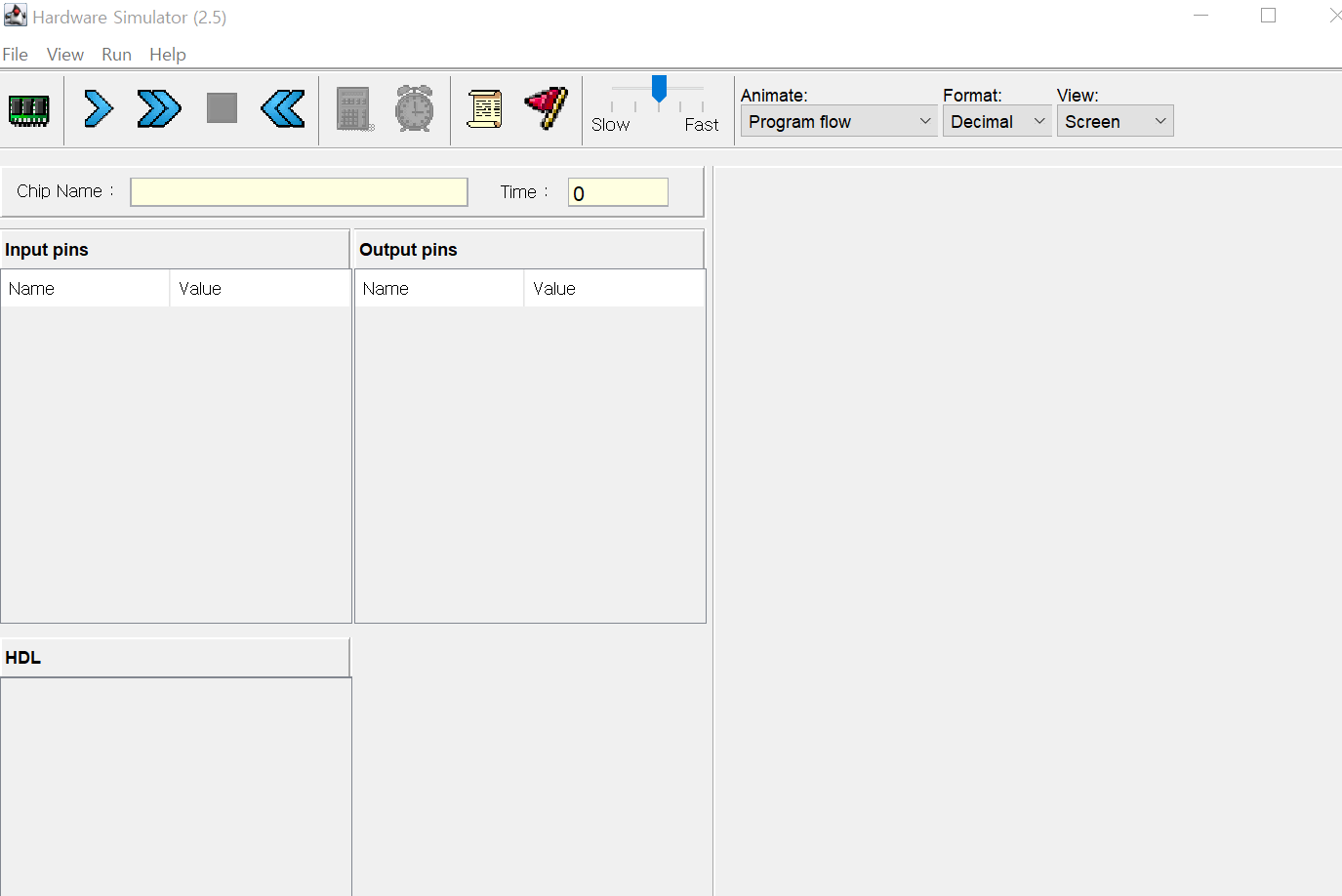

압축 풀고 tools에 들어오면

hardware simulator로 시작하면 되는데

자바 개발 키트 jdk 설치 안했다고 이런 경고창이 나온다.

jdk에는 오라클 jdk랑 open jdk가 있는데

오라클 jdk는 몇년 전부터 유료화 됬으니까 (개인으로 써도 괜찬은진 몰르겟다.)

그냥 공짜인 open jdk 다운받아서 쓰려고한다.

다운 설정하는 방법은 검색하면 금방 나오니 pass

------

하려했는데 나도 자바 설치하는법 잊어서 찾아봤다

이 글은 쓴지 좀오래되서 jdk 버전 13인데, 지금 openjdk 사이트 들어가면 18버전을 다운받을수 있다.

https://recipes4dev.tistory.com/173

예전에 자바 웹개발자 과정 수업 들으면서 자주 했었던건데 오랜만에 한다.

자바 설치랑 환경변수 잘 등록하고

다시 hadware simulator를 실행해보자

그러면 콘솔창이 갑자기 떳다 사라지면서 조용해진다.

잘못 된줄 알았는데 조금 기다렸더니 곧 시뮬레이터 창이 뜬다.

첫 번째 장에서 구현해야할 하드웨어 칩으로는

Nand, Not, And, Or/XOr, 멀티플렉서, 디멀티플렉서, 멀티비트/다중통로 게이트/먹스 들을 만들면 된다.

책 상에는 빌트인(이미 구현된) 칩과 이 빌트인 칩을 왜 쓰는지 어떻게 불러오는지 설명이 있긴한데

nand2tetris 사이트에 들어가면 책 나오니까 거기 내용 번역해서 보거나 번역서 보면 나와있다.

일단 바로 기본 논리게이트 구현부터 해보자

일단 1장에서 구현해야할 논리게이트는 난드를 제외한 15가지가 있는데,

* Nand - 난드 게이트의 경우, 이 프로젝트가 nand 게이트를 이용하여 쌓아올라가는것 만큼 기본 게이트로 제공하여 구현안해도 된다. 이걸로 다른 게이트들 만들고, nand로 만든 여러 게이트들로 조합 -> 순차논리회로->CPU까지 만들어간다.

아래의 15가지 기본 논리 게이트를 구현하면 된다!

1. Not

2. And

3. Or

4. Xor

5. Multiplexer

6. Demultiplexer

7. Multi-bit Not(16bit)

8. Multi-bit And(16bit)

9. Multi-bit Or(16bit)

10. Multi-bit multiplexer(16bit)

11. Multi-way Or(8way)

12. Multi-way Demultiplexer(4way)

13. Multi-way Demultiplexer(8way)

14. Multi-way/Multi-bit multiplexer(4way 16bit)

15. Multi-way/Multi-bit multiplexer(8way 16bit)

nand2tetris에서는 HDL 하드웨어 기술 언어로 논리 회로를 작성하면 되고

(책 부록 참조)

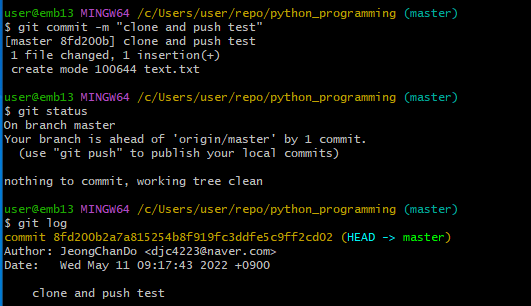

논리 게이트를 구현하고 테스트 하는 방법은

아래의 projects/해당챕터/*.hdl 파일을 텍스트 에디터로 작성후에

하드웨어 시뮬레이터로 아래의 projects/해당챕터/*.hdl 파일과 *.tst를 로드해서 실행하면 된다.

- project 파일 유형 정리 -

*.hdl : 논리 게이트 인터페이스(입출력이 뭔지), 동작 정의

*.tst : 테스트를 위한 스크립트. *.hdl을 실행한 결과가 *.cmp 파일과 동일한지 보고, 에러없이 일치하면 맞게 구현한것

*.cmp : hdl 파일과 tst 파일로 실행한 결과가 맞는지 비교하기 위한 파일

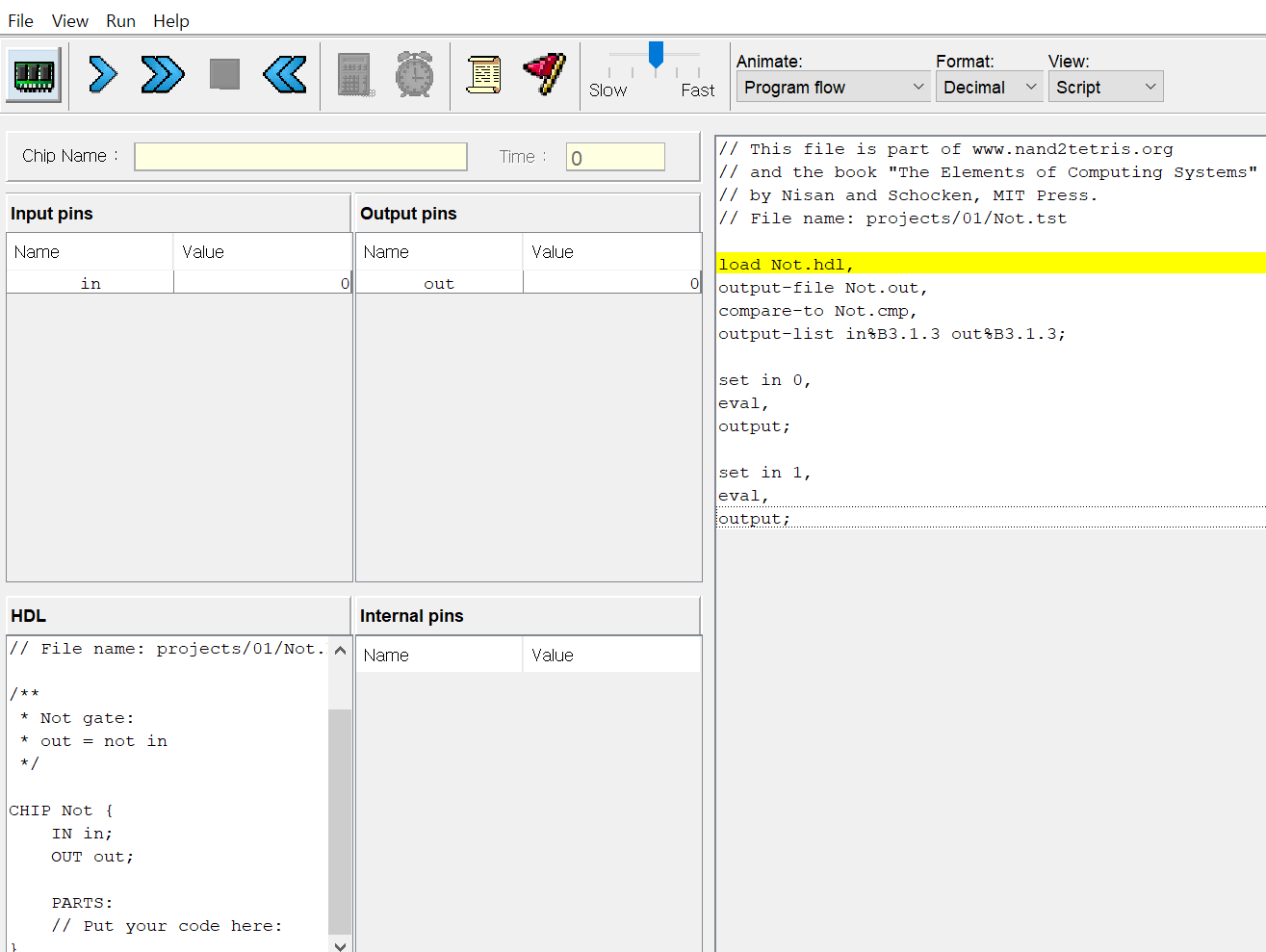

not.hdl과 not.hdl 테스트를 위한 not.tst을 로드하면 아래의 사진처럼 나오는데

텍스트 에디터로 클래스 정의하듯이 작성하자.

CHIP 논리회로명{

입력단자 a, b, ...

출력단자 out, ...

PARTS:

이미 구현된 게이트 or 빌트인 NAND 등으로 원하는 연산이 뜨도록 작성

}

이 책에서는 인터페이싱, abstract이라고 자주 표현이 자주 나오는데

여기서 말하는 인터페이스란 입력이 몇 개고 어떤 이름으로 들어오고, 출력은 무슨 이름으로 어떻게 나오는지를 말한다.

여기서 나오는 과제들은 *.hdl 파일에서 인터페이스 내용들은 이미 정의되어 나오니

해당 회로가 원하는 동작을 할수 있도록 PART에서 OUT이 원하는 데로 나오도록 회로들을 잘 연결해주면 된다.

일단 Not 게이트부터 시작해보자

1. Not

- 입력 : in

- 출력 : out

- 동작 : 입력을 반전시키면 된다

막상 시작하려고 하니까 nand 게이트로 이걸 어떻게 만드나 싶다.

not은 입력이 1개고, nand는 2개인데? 책에서 말하기를 난드 하나로 만들수 있다고한다.

난드 게이트 진리표를 보고 조금 생각해보니 알거같다.

x1과 x2에 똑같은 입력이 들어가면, 입력이 0일때 출력이 1, 입력이 둘다 1일때 0인게 보이니까.

Not의 in을 하나의 난드게이트 x1, x2에 바로 연결해주고

Not의 out과 난드게이트 F를 연결해주면 되겠다.

* 아까 빌트인 nand 게이트를 쓴다고 했는데 우리는 nand 게이트가 어떻게 구현됬는지 알필요 없이

입출력이 어떻게 되는지(=인터페이스)만 보면된다

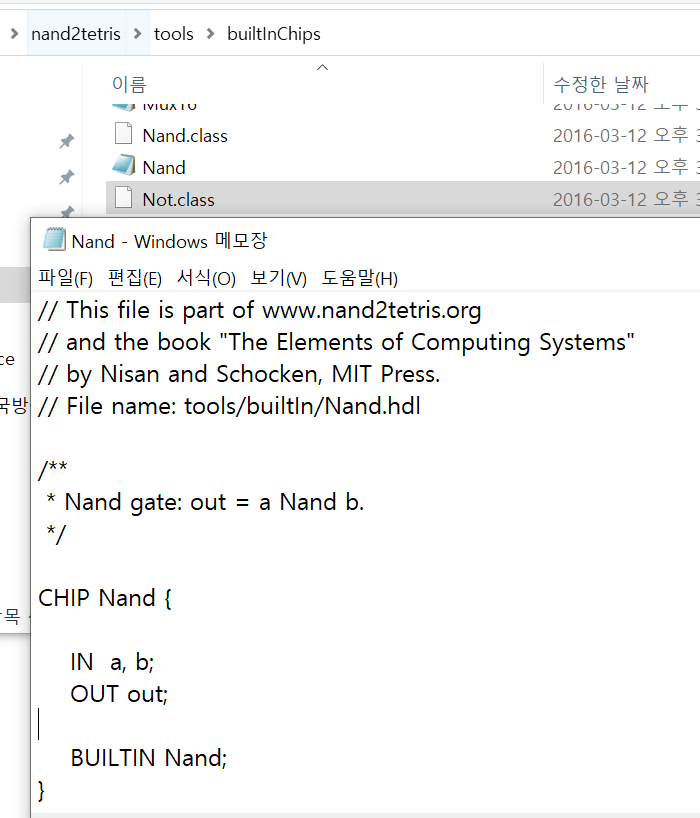

빌트인 칩들은 tools/builtinChips에 존재한다.

구현 내용인 PARTS는 없고 입출력을 제외하면 BULTIN Nand;만 보이는데 Nand.class의 내용을 읽어서 처리하나보다.

이제 Nand 게이트가 어떻게 되어있는지 봤고, Nand로 Not게이트를 어떻게 만드는지도 알았다.

그럼 텍스트 에디터로 not.hdl을 열어서 수정하자.

나는 vs코드나 다른게 없어서 그냥 메모장에다가 했다.

주의 사항은 ';'을 빼먹은것처럼 문법을 틀린경우 칩이 로드되지 않는다.

Nand 게이트로 Not.hdl을 구현하고

CHIP Not {

IN in;

OUT out;

PARTS:

Nand(a=in, b=in, out=out);

}

테스트 스크립트를 돌리면 에러없이 입력핀이 0일때 출력핀은 1, 반대의 경우도 잘 나온다.

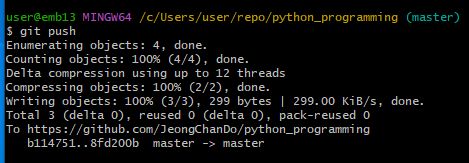

2. And

- And 게이트는 간단하다.

- 난드게이트에 A, B를 넣은 후 앞에 구현한 Not 게이트의 in에다가 넣어주면 끝.

* hdl 을 작성할때 언더스코어 _를 썻더니 로드가 안된다. 아무래도 매개변수 자리에는 특수문자를 넣으면안되나보다.

CHIP And {

IN a, b;

OUT out;

PARTS:

// Put your code here:

Nand(a=a, b=b, out=notIn);

Not(in=notIn, out=out);

}

3. Or

or 게이트에서 부터 어떻게 해야할지 머리가 아프기 시작한다.

고민해서 만들 시간 없으니 검색해서 만들자.

- 책에서는 and랑 not 게이트로 만들수 있다고하는데, nand만으로도 or를 만들수 있다. 근데 책대로 해야지

위 그림과 똑같이 hdl를 작성하면

CHIP Or {

IN a, b;

OUT out;

PARTS:

Not(in=a, out=aOut);

Not(in=b, out=bOut);

And(a=aOut, b=bOut, out=andOut);

Not(in=andOut, out=out);

}

역시 or 게이트도 잘 동작된다.

그런데 하다보니까 이렇게 에러 안뜨고 잘 넘어가면 되는건지 아리까리하다

다시 책보면 되긴한데 몇일 내내 원서로 보다보니 눈에 잘 들어오지는 않아서

그냥 한번 마지막 Not을 빼고 and 출력을 out으로 해봤다.

역시나! 잘못 출력이 나온때부터 테스트는 멈춘다.

다음으로 넘어가기를 눌러줘야 테스트 스크립트가 아래로 가는데 원하는 결과랑은 다르게 나온다.

앞으로 남은 1장 게이트는 13개.. 이거 왜이렇게 많냐

다른 챕터는 복잡하긴 해도 구현할게 적은데

내용을 줄이던가 해야되겟다.

4. Xor

5. Multiplexer

6. Demultiplexer

7. Multi-bit Not(16bit)

8. Multi-bit And(16bit)

9. Multi-bit Or(16bit)

10. Multi-bit multiplexer(16bit)

11. Multi-way Or(8way)

12. Multi-way Demultiplexer(4way)

13. Multi-way Demultiplexer(8way)

14. Multi-way/Multi-bit multiplexer(4way 16bit)

15. Multi-way/Multi-bit multiplexer(8way 16bit)

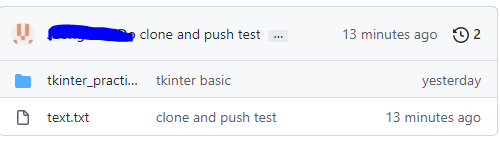

'컴퓨터과학 > 디지털회로' 카테고리의 다른 글

| nand2tetris - 6. hack 기계어와 어셈블리어 1 (0) | 2022.05.16 |

|---|---|

| nand2tetris - 5. 레지스터와 RAM 구현하기 (0) | 2022.05.15 |

| nand2tetris - 4. 반가산기부터 ALU까지 구현하기 (0) | 2022.05.15 |

| nand2tetris - 3. 4way/8way 16bit muletiplexer까지 기본논리회로 마무리 (0) | 2022.05.15 |

| nand2tetris- 2. Xor부터 8way Demultiplexer까지 (0) | 2022.05.15 |